# ISSN: 2454-9940

# INTERNATIONAL JOURNAL OF APPLIED SCIENCE ENGINEERING AND MANAGEMENT

E-Mail : editor.ijasem@gmail.com editor@ijasem.org

### Using the gm/ID Approach, a Folded Cascode OTA is Designed for Use in a Variety of Service Areas

Ms. G.DHANA LAKSHMI, Mrs. C. Bharathi, Mrs. MADISA LALITHA

*Abstract* — In this study, we provide a systematic approach to the design of folded cascode operational transconductance amplifiers. In order to maximize the efficiency of the MOS transistors, the design is carried out in three distinct zones of operation (weak inversion, strong inversion, and moderate inversion) according to the gm/ID technique.

The developed folded cascode OTA operates in strong inversion mode with a unity-gain frequency of 430MHz and a DC gain of 77.5dB using a 0.35m CMOS technology. It offers a 92dB DC gain and a gain bandwidth product of around 69MHz when operating in a mild inversion mode. DC gain of 75.5 dB and unity-gain frequency are also characteristics of the OTA circuit.

In order to construct a Sigma Delta ADC for broad band radio applications, we set out to create a folded cascode OTA circuit.

This paper will proceed as described below. In Part II, we dissect the OTA structure of a folded cascode. The OTA circuit architecture for the three operating ranges is shown in Section III. Section IV provides a scope for the design. After comparing our research to other studies, we provide some final thoughts. weak inversion area restricts frequency to 19.14 MHZ.

#### **II. COMPACT OTA STRUCTURE**

A. Folded Cascode OTA, CMOS IC design, and g / I

#### B. NMOS Input Transistor INTRODUCTION

M. D The gain of the operational amplifier is produced by its input stage. Since the NMOS device is more mobile, the input differential pair of a PMOS device experiences less noise. The evolution of the microelectronics sector has been marked by ever-increasing integration and complexity. Linear miniaturization of integrated circuit design characteristics is the target. Value of The design's intricacy is one of the main obstacles stopping this progression in its tracks. Building a reliable analogue IC requires the skill of an experienced designer. Although numerous tools have emerged over the years to help automate the topology synthesis [1]-[4], it is ultimately up to the designer to decide which circuit architecture is most suited to satisfy the needs. In [5], we see the establishment of a successful heuristic approach to optimization. References [6]-

[7] cover the literature on nominal circuit design, [8–10] cover size concerns, and [11–13] cover worst-case optimization. There are a number of optimization programs available, including the equation-based GPCAD [14, 15], the symbolic-based AMG [16, 17], and the simulation-based ASTRX/OBLX [17, 18]. Multiple recent articles ([13], [19]-[24]) have addressed the size problem from a variety of angles. While we have made strides toward lower supply voltages and higher frequencies, it is still difficult to develop high-performance base band analog circuits. Software-based radio receivers that anticipate an after-antenna RF signal conversion are now popular.

### <u>dhanalaxmi959@gmail.com, chamarthibharathi@gmail.com</u> <u>lalithamadisa@gmail.com</u>

Gonna Institute of Information Technology and Sciences (GIITS)

Therefore, a substantially greater sampling frequency and resolution are required in the design of the analog-to-digital converter. In this case, the OTA is a an essential component of this kind of circuit, whether or not the switched capacitors method is employed to create the ADC. an NMOS pair with higher transconductance than the carrier. Because of this need for maximum gain, an NMOS transistor was used.

#### **B.** Analysis of the Structure

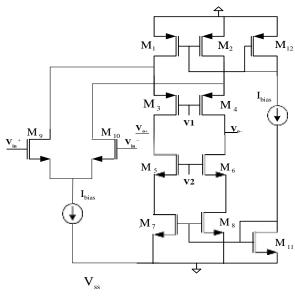

The operational amplifier is the most time-consuming part of an analog circuit. The designer has a variety of OTA configurations to choose from, most of which are geared on raising the bar for performance expectations in design [25]. For its high gain and wide bandwidth, a "folded cascode" op-amp is our top pick. The folded cascode OTA is shown in Fig.1 (the term "folded cascode" refers to the modification of a diff-pair's Mosfets from p-channels to n-channels, thus the name).

A differential stage, made up of NMOS transistors M9 and M10, is essential to the functioning of the folded cascode OTA. Transistors M1, M2, M7, and M8 get their DC bias voltages from mosfets M11 and M12. Gain bandwidth and open-loop voltage gain are defined as follows: (1)

A = g m9.g m6.g m4 V I 2 g 2 + g 2 D m 4 N m 6 P (1)

GBW = g m9 ID

ID C L (2)

Where gm4, gm6, and gm9 are the transconductances of the M4, M6, and M9 transistors, respectively. Mosfets M4, M6, and M9 all have a bias current, denoted by ID. The parameters N and P refer to channel length modulation for NMOS and PMOS devices, respectively; CL denotes the capacitance at the output node. With M4 and M6 transistors' complementary nature in mind:

gm4 = gm 6 (3)

This leads to the following gain expression: A = g m 9. g m 6 V I 2 2 + 2 D N P (4)

#### Twelfth, a folded cascade OTA layout

Different aspects of the op-amp's functionality—such as its open-loop voltage gain, unity-gain bandwidth, slew rate, noise, and so on—are what set it apart. These performance metrics, such as transistor size, bias currents, and other component quantities, are hardcoded into the design [26].

Finding the optimal values for design parameters that nevertheless adhere to requirements and other guidelines is the

Fig. 1 Folded cascode OTA topology

focus of this effort. In this work, we present the layout of a foldable cascode OTA amplifier that can function in one of three frequency bands. The gm/ID approach proposed by Flandre and Silveira [27] is used in this design's synthesis technique.

A Measurement Formulation

To better understand the top-down synthesis process for CMOS OTA structures, a design flow has been created (Fig. 2). In reality, this last step begins with setting the criteria to optimize, such gain and unity gain frequency, so that MOS device sizes and bias current may be calculated.

• gm9 may be calculated directly from the transition frequency and capacitive load using equation (2), whereas gm9/ID can be calculated using equation (4) utilizing the supplied DC openloop gain and the selected technology. The bias current, ID, may be calculated using either gm9 or gm9/ID, and gm9/ID also returns I', where I'= ID/(W /L).

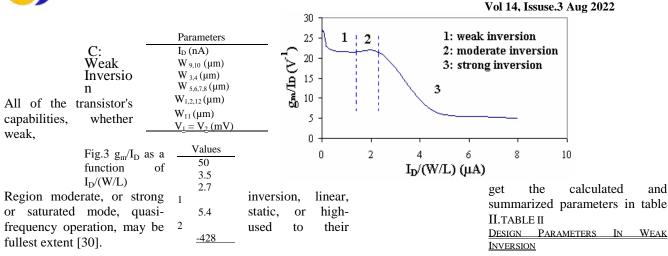

ID/I' provides the final answer for W/L To use the aforementioned technique and calculate the design parameters (Fig. 3), we take advantage of the fact that the CMOS technology at hand (0.35m of AMS) exhibits a universal gm/ID as a function of ID/(W/L). This feature is gained by modeling and is formally specified in the

In analogue circuits, the transistors are often biased in the saturation state. However, either strong or weak inversion may be used to run them. Biased in weak inversion, transistors give more gain with less current and have a greater transconductance. The thermal noise produced by these transistors is minimal. We want to provide a method to analyze folded cascode OTA performance across all three modes of operation.

D. Weak Inversion Design

Weak inversion exhibits larger gm/ID values with lower current, as illustrated in Fig. 4. Consequently, a greater gain is preferable for this working mode.

Our requirements for the circuit shown in Fig.1 are listed in Table I.

| TABLE I             |            |

|---------------------|------------|

| SPECIFICATIONS      |            |

| Specifications      | Values     |

| $A_v (dB)$          | 105        |

| GBW (MHz)           | 21.5       |

| $C_L(fF)$           | 10         |

| $V_{dd}/V_{ss}(V)$  | $\pm 1$    |

| Channel length (µm) | <u>1</u>   |

| Applying the        | previously |

elucidated design technique, we

with the BSIM3V3 MOSFET model. The circuit denotes an offset voltage of 0.4mV, a Slew Rate of 3.3V/µs, a wide input common-mode range of [-0.99V, 0.98V], a wide output common-mode range between -0.96V and 0.95V. It consumes 0.6µW.

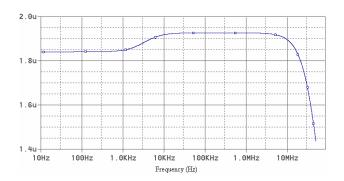

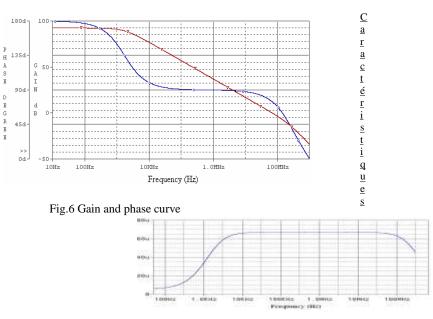

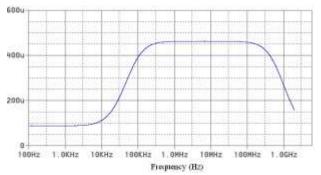

Moreover, our device is able to achieve a degrading gain of 75.5dB, a bandwidth of 19.14MHz with phase margin of 67degrees (Fig.4), a good common mode rejection ratio of 126.8dB and a low transconductance of 1.8µS kept constantfor a wide range of frequency (Fig.5).

Similarly, the design technique mentioned in Section A is used to ensure that the tiny signals model remains over all sections of the transistor's unchanged operational spectrum. The discovered design parameters

TABLE

SPECIFI CATION

Ш

S

Specifications

$A_v(dB)$

GBW (MHz)

$C_L(pF)$

$V_{dd}/V_{ss}\left(V

ight)$

Channel length (µm)

ISSN2454-9940www.ijsem.org

and

WEAK

Values

100

70

0.1

+2

1

The designed folded cascode OTA is biased at  $\pm 1V$ powersupply voltage using CMOS technology of 0.35 µm of AMS

Fig.5 OTA's transconductance in weak inversion region

Moderate Inversion C. Design *Consequently,* the gain bandwidth product isn't increased and essential enough to suit wide band applications since we get excellent performances with extremelv low consumption in weak inversion.

We will analyze the OTA's design in the mild inversion zone to see if we can increase this parameter while maintaining the same level of energy efficiency. In order to further restrict the bandwidth product of the OTA gain, we suggest the requirements shown in table III.

| De <u>sign</u> | PARAMETERS | IN | MODERATE |  |

|----------------|------------|----|----------|--|

| INVERSIO       | ON         |    |          |  |

| KSION               |        |     |

|---------------------|--------|-----|

| Parameters          | Values |     |

| $I_D(\mu A)$        | 2      |     |

| W 9,10 (µm)         | 9      |     |

| $W_{3,4}(\mu m)$    | 2      | 2.7 |

| W 5,6,7,8 (µm)      | 1      |     |

| $W_{1,2,12}(\mu m)$ | 5      | 5.4 |

| $W_{11}(\mu m)$     | 2      |     |

| $V_1 = V_2 (mV)$    | -256   | _   |

|                     |        |     |

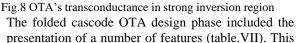

Fig.6 shows that the OTA circuit can achieve a DC gain of 92dB, a unity-gain frequency of 69MHz, and a phase margin of 74.5degrees. Figure 7 depicts its transconductance value of around 65 S. It loses 48 mW of power.

Gain and GBW characteristics are intriguing in this behavior mode, as are the broad input and output swings that are preserved.

| Fig.7 OTA's transconductance in moderate inversion region | V                    |

|-----------------------------------------------------------|----------------------|

| C. Layout for Extreme Inversion                           | <u>a</u><br>1        |

| We estimate that bandwidths fulfilling the needs of       | <u>1</u><br><u>e</u> |

| wide band applications may be attained even in weak       | <u>u</u>             |

| inversion and for relatively large bias current.          | <u>r</u>             |

| In this current range, we see that the gm/ID ratio        | <u>s</u>             |

| put in a                                                  |                      |

| ISSN2454-9 | 940www.ijsem.org |

|------------|------------------|

| Vol 14, I  | ssuse.3 Aug 2022 |

specifications given by table V.

T A B L E V S P

E C

> C A T

I O

N

S

| $A_v$ (dB)                       | 80         |

|----------------------------------|------------|

| GBW (MHz)<br>C <sub>L</sub> (pF) | 450<br>0.1 |

| $V_{dd}/V_{ss}(V)$               | $\pm 2$    |

| Channel length (µm)              | 1          |

The design process yields the Mosfets' sizes (table VI). The results of strong inversion, we conclude, are more relevant than those of weak and moderate inversion, and this is because strong inversion makes advantage of high current to TABLE VI

| DESIGN PARAMETERS IN STRONG INVERSION |

|---------------------------------------|

|                                       |

| ESIGN LAKAMETERS | STRONG INVERS            | ION  |

|------------------|--------------------------|------|

| Parameters       | Values                   |      |

|                  | $I_D(\mu A)$             | 27.5 |

|                  | W <sub>9,10</sub> (µm)   | 14   |

|                  | $W_{3,4}(\mu m)$         | 5.4  |

|                  | W 5,6,7,8 (µm)           | 2    |

|                  | W <sub>1,2,12</sub> (µm) | 10.8 |

|                  | W <sub>11</sub> (µm)     | 4    |

| $V_1 = V_2 (mV)$ | -318                     |      |

|                  |                          |      |

Featuring a huge unity-gain frequency of 430MHz and a phase margin of 58.2degrees, the folded cascode OTA has a gain of 77.5dB. Approximately 396 S may be transducted via it (Fig. 8).

architecture is functional in a wide range of frequencies. The transistor operating mode is determined by the requirements of the application. VISUALIZATION PANEL XII

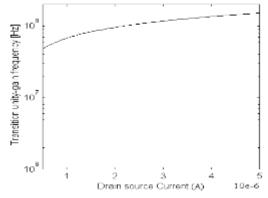

We use the MATLAB tool to show a design window in several areas of operation, each of which produces a unique pair of (Ft, ID) values that may be used to check certain design parameters, such as the unity gain frequency and the drain source current.

In strong inversion, a drain current of 27.5A results in a unity-gain frequency of 460MHz, as shown in Figs.9 and 10. For a constant 2A current, the GBW value is close to 90MHz when the inversion is modest.

In the mild inversion area, we see that the unity gain frequency rises, thus we must account for the modification of the signals model in this region strong inversion current reach other places.

Fig.9 Unity gain frequency as a function of drain source

Fig.10 Unity gain frequency as a function of drain source current inmoderate inversion region

- III. Results Comparisons (XII)

- We will compare our research to IV. previous studies after we explain the various OTA design factors. This paper compares the folded cascode OTA's performance to that of two recently designed OTA circuits. Class-AB OTAs are the initial kind [29].Second, in [30], а telescoping OTA design was introduced. Table VIII provides this contrast. It can be easily observed that a low power, low voltage topology with a high static gain may be attained by using a folded cascode OTA design.

#### XVI. CONCLUSIONS

As a result, the synthesis of high-performance analog integrated circuits is a challenging endeavor that requires expert knowledge of a wide range of topics. Therefore, the skill set of the analog designer is still highly sought for. To achieve high gain and wide bandwidth, this paper discusses the strategy design of a folded cascode OTA operating in weak inversion, strong inversion, and moderate inversion.

We predict that the gm/ID approach is widely used for sizing in a variety of operational modes, allowing for the highest possible performance with any given technology.

Using these findings on folded cascode OTA for low consumption and broad band applications in wide band A/D converters is a potential direction for further research.

| TABLE VII                         |

|-----------------------------------|

| FOLDED CASCODE OTA SPECIFICATIONS |

| Specifications   | Weak inversion | Moderate inversion | Strong inversion |

|------------------|----------------|--------------------|------------------|

| <br>DC Gain (dB) | 75.57          | 92                 | 77.53            |

#### ISSN2454-9940www.ijsem.org Vol 14, Issuse.3 Aug 2022

| GBW (MHz)              | 19.14         |   | 69            | 430           |

|------------------------|---------------|---|---------------|---------------|

| Transconductance (µS)  | 1.8           |   | 65            | 396           |

| Phase margin (degrees) | 67            |   | 74.5          | 58            |

| Offset voltage (µV)    | 430.4         |   | 246           | 337           |

| Output swing (V)       | [-0.96; 0.95] |   | [-1.94; 1.84] | [-1.84; 1.72] |

| Input swing (V)        | [-0.99; 0.98] |   | [-1.95; 1.87] | [-1.95; 1.87] |

| Slew Rate (V/µs)       | 3.3           |   | 16.5          | 196           |

| CMRR (dB)              | 126.8         |   | 133           | 114           |

| PSRR p, n (dB)         | 18            |   | 45.7          | 46.5          |

| Supply voltage (V)     | ±1            |   | $\pm 2$       | $\pm 2$       |

| Bias current (µA)      | 0.1           | 4 |               | 55            |

| Power consumption (µW) | 0.6           |   | 48            | 660           |

TABLE VIII

PERFORMANCES COMPARISON

| Performance/Design     | Yao & Steyaert [29] | Craig Brendan Keogh [30] | This work      |

|------------------------|---------------------|--------------------------|----------------|

| OTA Architecture       | Class-AB            | Telescopic               | Folded cascode |

| Technology (µm)        | 0.09                | 0.18                     | 0.35           |

| DC Gain (dB)           | 50                  | 79                       | 75.57          |

| GBW (MHz)              | 57                  | 8.5                      | 19.14          |

| Phase margin (degrees) | 57                  | 78                       | 67             |

| Supply voltage (V)     | 1                   | 0.925                    | 1              |

| Power consumption (µW) | 80                  | 4.6                      | 0.6            |

#### REFERENCES

According to [1] "IDAC: An Interactive Design Tool for Analog CMOS Circuits," M.G.R. Degrauwe et al., IEEE J.Solid-State circuits, vol. sc-22, no. 6, dec.(1987), pp. 1106-1116, you can get more information about this.

According to [2] "OASYS: A framework for analog circuit synthesis," published in IEEE Trans. Computer-Aided Design, vol. 8, no. 12, Dec. (1989), pp. 1247-1266, R.Harjani, R.A. Rutenbar, and L.R. Carley contributed to this article.

"OPASYN: a compiler for CMOS operational amplifiers," by H. Y. Koh, C.H. Séquin, and P.R. Gray, was published in the December 1990 issue of the IEEE Transactions on Computer-Aided Design (vol. 8, no. 12), pages 113-125.

(4) "STAIC: An interactive framework for synthesizing CMOS band BiCMOS analog circuits," IEEE Trans.Computer-Aided Design, volume 11, issue 11, November 1992, pages 1402-1417, J.P. Harvey, M.I. Elmasry, and B. Leung.

[5] "Optimizing performances of switched current memory cells through a heuristic," Journal of Analog Integrated Circuits and Signal Processing, Springer Editor, (2006), M. Fakhfakh, M. Loulou, and N. Masmoudi.

Reference: [6] "A survey of optimization techniques for integrated-circuit design," Proc. IEEE, vol. 69, no. 10, Oct. 1981, pp. 1334-1364; R.K. Brayton, G.D. Hachtel, and A.L. Sangiovanni-Vincentelli.

According to [7] "DELIGHT.SPICE: An optimization-based system for the design of integrated circuits," published in IEEE Trans.Computer-Aided Design, vol. 7, no. 4, Apr. (1988), pp. 501-519, by W. Nye et al.

"The simplicial approximation approach to design centering," IEEE Trans. Circuits Syst. I, vol. Cas-29, no. 2, February (1982), pp. 88-96, S.W. Director and G.D. Hachtel.

According to [9] "Design centering by yield prediction," by

K.J.Antreich and R.K. Koblitz, published in IEEE Trans. Circuits Syst. I, volume Cas-29, issue 2, February (1982), pages 88-96.

For example, see [10] "Integrated circuit quality optimization using surface integrals," IEEE Trans. Computer-Aided Design, vol. 12, no. 12, Dec. 1993, pp. (1868-1879) by Paul Feldmann and Stephen W. Director.

Circuit analysis and optimization driven by worst-case distances," [11] K.J.Antreich, H.E. Hraeb, and C.U. Wieser. Articles 57-71 from the January 1994 issue of IEEE Transactions on Computer-Aided Design.

"Worst-case analysis and optimization of VLSI circuit performances," [12] A. Dharchoudhury and S.M. Kang. April 1995, issue 14(4) of the IEEE Transactions on Computer-Aided Design, pages 481–492.

[13] A. Burmen et al., "Automated robust design and optimization of integrated circuits by means of penalty functions," int. J. Electron. Comm.,57, no. 1, (2003), pages 47-56.

"GPCAD: A tool for CMOS op-amp synthesis," 1998 IEEE/ACM Int. Conf.Computer-Aided Design, New York, (1998), pp. 296-303. [14] M. del Mar Hershenson, S.P. Boyd, and T.H. Lee.

For example, see [15] "Optimal design of a CMOS op-amp via geometric programming," IEEE Trans. Computer- Aided Design, volume 20, issue 1, January (2001), pages 1-21, by M. del Mar Hershenson, S.P. Boyd, and T.H. Lee.

Based on the work of G. Gielen et al., "An analogue module generator for mixed analogue/digital ASIC design," published in Int. J.Circuit theory and App.,vol. 23, no. 4, July-Aug. (1995),pp.269-283.

"Analog circuit design optimization based on symbolic simulation and simulated annealing," IEEE J. Solid-State circuits, volume 25, issue 3, June (1990), pages 707-713;

G.G.E. Gielen, H.C.C. Walscharts, and W.M.C. Sansen.

[18] "Sunthesis of high- performances analog circuits in ASTRX/OBLX," IEEE Trans. Computer-Aided Design, volume 15, issue 3, March (1996), pages 273-294; E.S.Ochotta, R.A. Rutenbar, and L.R. Carley.

"Efficient analog circuit synthesis with simultaneous yield and robustness optimization," 1998 IEEE/ACM, Int. Conf. Computer-Aided Design, New York, (1998), pages 308-311.

(See: [20] R. Schwencker et al., "Automating the sizing of analog CMOS circuits by consideration of structural constraints," DATE Conf. And Exhibition, 1999, Los Alamitos, (1999), pp. 323-327.

According to [21] R. Phelps et al., "Anaconda: simulation-based synthesis of analog circuitsvia stochastic pattern search," IEEE Trans. Computer-Aided Design, volume 19, issue 6, June 2000, pages 703-717.

Based on the work of T. Mukherjee, L.R. Carley, and R.A. Rutenbar, "Efficient handling of operating range and manufacturing line variations in analog cell synthesis," published in IEEE Trans. Computer-Aided Design, volume 19, issue 8, August 2000, pages 825-839.

According to [23] F. Schenkel et al., "Mismatch analysis and direct yield optimization by spec-wise linearization and feasibility-guided search," Proc. 38th DAC, New York, (2001), pp. 22-38.

The following is a direct quote from "CMOS op-amp sizing using a geometric programming formulation," written by P. Mandal and V. Visvanthan and published in IEEE Trans. Computer-Aided Design volume 20, issue 1 (January 2001), pages 22-38.

Reference: [25] Behzad Razavi, "Design of Analog CMOS Integrated Circuit", TheMcGraw-Hill Companies, Inc., United States, (2001), ISBN:0-07- 118815-0.

[26] Conception and Optimisation of a Rail-to-Rail CMOS Variable-Tension Operational Amplifier, M. Loulou, S. Ait Ali, and N. Masmoudi.

Faible Consommation," Journal of Scientific Research in Lebanon, published by the National Council for Scientific Research in Lebanon, Volume 4, Number 1 (2003): pages 75–90.

[27] Silveira, D. Flandre, and P.G.A. Jespers, "A gm/ID based methodology for the design of CMOS analog circuits and application to the synthesis of an SOI micropower OTA", IEEE J. of Solid State Circuits, vol. 31, no. 9, sept. (1996).

[28] "Fully Differential Operational Amplifier with Accurate Output Balancing," IEEE Journal of Solid State Devices, Vol. 23, No. 6, pp. December (1990), by M. Banu, J. M. Khoury, and Y. Tsividis.

[29] The article "A 1-V 140-W 88-dB Audio Sigma-Delta Modulator in 90-nm CMOS" by Y. Libin, M. Steyaert, and W. Sansen was published in the November 2004 issue of the IEEE Journal of Solid State circuits.

In his article "Low-Power Multi-Bit -Modulator Design for portable Audio Application," Craig Brendan Keogh presented research from Stockholm in March 2005.