E-Mail: editor.ijasem@gmail.com editor@ijasem.org

www.ijasem.org

# A NEW STRUCTURE WITH NEW ALGORITHMS FOR CASCADED MULTILEVELBINVERTERS BY REDUCING NUMBER OF IGBT

NUTALAPATI TIRUMALA RAO¹, Y. RAJASEKHAR REDDY²

ABSTRACT: In this paper, a new structure for cascade multilevel inverter is presented which consists of a series connection of several sub-multilevel units. Each sub-multilevel unit comprises of eight unidirectional switches, two bidirectional switches, and six DC voltage sources. For the proposed cascade topology, two algorithms are presented to produce all possible levels at the output voltage waveform. The required analysis of the voltage rating on the switches is provided. In order to verify the performance of the proposed inverter, the experimental results for a 15-level inverter are provided. The experimented 15-level inverter is compared with the other presented inverters in literature in terms of the number of DC voltage sources, switches, drivers, and blocked voltage by switches. The results of comparisons indicate that the experimented 15-level inverter requires lower power electronic elements. Moreover, the blocked voltage on the switches of the proposed topology is less than other topologies.

### INTRODUCTION

IN recent years, the application of multilevel inverters in electrical industry such as renewable energy machine drives, and power quality devices have been increased. Multilevel inverter is a power electronic system which can produce a stepped waveform at output voltage. As the number of output voltage levels is increased, the total harmonic distortion of output voltage is increased and the voltage stress on semiconductors is reduced [1-3]. Two-level inverter was the first topology which consists of two power switches and one DC voltage sources. This topology is suitable for low voltage applications. The voltage stress on the switches of two-level inverter is high and equal to the amplitude of input DC voltage source. Moreover, the switching losses and harmonic distortion of output voltage and current waveforms are high [4, 5]. To solve

these problems, conventional multilevel inverters were introduced which have been named • Flying capacitor multilevel inverter, • Diode-clamped multilevel inverter, • Cascade multilevel inverter. The mentioned structures use similar numbers of switches. However, the number of onstate switches in current path in the flyingcapacitor and diode-clamped multilevel inverters is less than cascade topology which reduce the conduction switching losses. Using high numbers of capacitors and diodes are the main disadvantages of flying capacitor and diode-clamped multilevel inverters. Also, balancing the voltage of capacitors in flving capacitor and diode-clamped multilevel another inverters is disadvantage. The cascade multilevel inverter uses a

large number of DC voltage sources for producing higher levels which increase the circuit size and converter cost [6-8]. In order to improve, the power electronic parameters in conventional multilevel inverters, many structures have been presented by researchers. A basic ladder structure has been presented in [9] which include several DC voltage sources along with common-emitter bidirectional switches. In this structure, in order to produce any levels, there are only four switches in current path. However, this topology requires many transistors and the voltage on switches is high. In [10], a new structure for multilevel inverter has been suggested which need low number of transistors and can be used in low voltage applications. In this topology, the number of on-state switches in current path increase with increasing the number of output voltage levels. Another multilevel inverter has been introduced in [11] which require lower transistors and the power loss is increased by increasing the number of output voltage levels. In order to reduce the number of drivers in the presented structures in [9-11], a ladder multilevel inverter has been presented in [12] which consists of several bidirectional switches and DC voltage sources. In this topology, by increasing the number of levels, the voltage on bidirectional switches increases which limits its applications in high voltage applications. In order to improve the power electronic parameters in the above mentioned structures, other structures have been presented in [13-21] which are the combination of presented multilevel inverters in [9-11]. presented structures in [9-11] are not suitable candidate for high voltage applications. In these structures, there are four high voltage switches which restrict their applications in high voltage applications. However, the presented structures in [15] and [16] are suitable for low voltage applications. All presented multilevel inverters in [9-16] require the same number of DC voltage sources. In

[17], another cascade multilevel converter topology based on series connection of several stages has been proposed in which each stage consists of two same basic units which are connected to each other using two unidirectional switches. This structure can produce any levels at output voltage waveform. In [18], another improved Hbridge multilevel converter topology has been proposed which is able to produce all levels. This topology uses a large numbers of IGBTs. In [19], a new symmetric multilevel converter structure with low voltage on switches and DC source has been presented. Other symmetric and asymmetric types for multilevel converters have been proposed in [20-21]. In this paper, a new cascade multilevel inverter based on the cascaded connection of 15level inverters has been proposed. The performance of the proposed structure is analyzed using a look-up table and mathematical analysis of voltage switches. The proposed 15-level inverter is compared with proposed 15-level inverters in [9-21] in terms of the number of transistors, drivers, DC sources, and onstate switches. Also, the performance of the proposed 15-level inverter is evaluated using experimental setup.

## PROPOSED SUB-MULTILEVEL

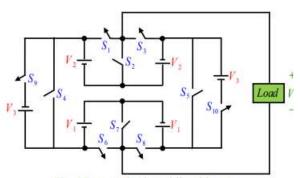

**INVERTER** The structure of the proposed sub-multilevel inverter is indicated in Fig. 1. As shown in this figure, the proposed structure comprises six unidirectional switches (S1, S3, S6, S8, S9, and S10), four bidirectional switches (S2, S4, S5, and S7) and six DC voltage sources. The proposed topology can be used for any values of resistive and inductive loads. The unidirectional switch consists of an IGBT along with an anti-parallel diode which requires only one gate driver circuit. The type of used bidirectional switch is common-emitter which includes series connection of two unidirectional switches. The used bidirectional switch requires one driver and can withstand both positive and negative voltage levels. By selecting the

values of DC voltage sources as V1=Vdc, V2=2Vdc, and V3=4Vdc, the proposed structure can produce 15 levels at output voltage waveform. The generated levels are 0,  $\pm Vdc$ ,  $\pm 2Vdc$ ,  $\pm 3Vdc$ ,  $\pm 4Vdc$ ,  $\pm 5$ Vdc,  $\pm 6$ Vdc, and  $\pm 7$ Vdc. The switching states of the proposed 15-level inverter are shown in Table 1. In this table, 0 and 1 mean that the switches are in OFF and ON states, respectively. As shown in this table, there are two states for generating the zero level. According to this table, it is clear that there are only three switches in current path at any levels which reduce the power losses such as switching and conduction losses. The value of blocked voltage by switches is an important parameter that affects the inverter cost. The standing voltage by the switch in OFF-state is named the blocked voltage by switch. The values of blocked voltage on the switches in the proposed 15-level inverter are calculated as follows

$$\begin{split} V_{S4} &= V_{S5} = V_{S9} = V_{S10} = 2(V_1 + V_2 + V_3) \\ V_{S4} &= V_{S5} = 2(V_1 + V_2) + V_3 \\ V_{S7} &= V_1 \\ V_{S6} &= V_{S8} = 2V_1 \\ V_{S2} &= V_2 \\ V_{S1} &= V_{S3} = 2V_2 \end{split}$$

Then, the total blocked voltage by all switches is:

$$V_{ST} = 6 V_{dc}$$

#### PROPOSED CASCADE MULTILEVEL INVERTER

There are four switches in the structure of the proposed sub-multilevel inverter which withstand maximum value of output voltage. This feature causes

Fig. 1 Proposed sub-multilevel inverter.

Table 1 The switching states of proposed 15-level inverter.

| States | ON and OFF switches |       |       |                       |       |       |       |       |       |          | Output          |

|--------|---------------------|-------|-------|-----------------------|-------|-------|-------|-------|-------|----------|-----------------|

|        | $S_1$               | $S_2$ | $S_3$ | <i>S</i> <sub>4</sub> | $S_5$ | $S_6$ | $S_7$ | $S_8$ | $S_9$ | $S_{10}$ | voltage $(V_o)$ |

| 1      | 0                   | 0     | 1     | 0                     | 1     | 0     | 0     | 1     | 0     | 0        | 0               |

|        | 1                   | 0     | 0     | 1                     | 0     | 1     | 0     | 0     | 0     | 0        |                 |

| 2      | 0                   | 0     | 1     | 0                     | 1     | 0     | 1     | 0     | 0     | 0        | $V_{dc}$        |

| 3      | 1                   | 0     | 0     | 1                     | 0     | 0     | 1     | 0     | 0     | 0        | -Vdc            |

| 4      | 0                   | 1     | 0     | 0                     | 1     | 0     | 0     | 1     | 0     | 0        | $2V_{dc}$       |

| 5      | 0                   | 1     | 0     | 1                     | 0     | 1     | 0     | 0     | 0     | 0        | -2Vdc           |

| 6      | 0                   | 1     | 0     | 0                     | 1     | 0     | 1     | 0     | 0     | 0        | $3V_{dc}$       |

| 7      | 0                   | 1     | 0     | 1                     | 0     | 0     | 1     | 0     | 0     | 0        | -3Vdc           |

| 8      | 0                   | 0     | 1     | 0                     | 0     | 0     | 0     | 1     | 0     | 1        | $4V_{dc}$       |

| 9      | 1                   | 0     | 0     | 0                     | 0     | 1     | 0     | 0     | 1     | 0        | -4Vdc           |

| 10     | 0                   | 0     | 1     | 0                     | 0     | 0     | 1     | 0     | 0     | 1        | $5V_{dc}$       |

| 11     | 1                   | 0     | 0     | 0                     | 0     | 0     | 1     | 0     | 1     | 0        | -5 V de         |

| 12     | 0                   | 1     | 0     | 0                     | 0     | 0     | 0     | 1     | 0     | 1        | 6Vdc            |

| 13     | 0                   | 1     | 0     | 0                     | 0     | 1     | 0     | 0     | 1     | 0        | $-6V_{dc}$      |

| 14     | 0                   | 1     | 0     | 0                     | 0     | 0     | 1     | 0     | 0     | 1        | 7Vdc            |

| 15     | 0                   | 1     | 0     | 0                     | 0     | 0     | 1     | 0     | 1     | 0        | $-7V_{dc}$      |

the suggested sub-multilevel inverter to be used in low voltage applications. Also, the proposed sub-multilevel can generate only 15 levels which is a limitation for generating higher numbers of levels. In order to increase the number of levels and using in high voltage applications, a new cascade multilevel inverter is presented The values of DC voltage sources in the suggested cascade inverter determine the number of generated levels at output voltage waveform. For this aim, two new algorithms for selecting the values of DC sources

**CONCLUSION** In this paper, a new structure for 15-level inverter was introduced firstly. Then, a cascade inverter based on the 15-level inverter was introduced. Two algorithms for selecting the amplitude of DC voltage sources were proposed. The proposed 15-level inverter

was compared with traditional multilevel inverters. The comparison results show that the proposed topology requires the least number of transistors, drivers, and DC voltage sources which causes the converter cost and volume to be reduced. Also, the number of on-state switches in current path in the structure of proposed topology is less than other topologies which causes the efficiency of the presented 15-level inverter to be high. In order to verify the performance of the proposed 15-level inverter. experimental results using a setup circuit are presented.

## REFERENCES

- [1] K. Gupta, A. Rajan, P. Bhatnagar, L. K. Sahu, and S. Jain, "Multilevel inverter topologies with reduced device count: A review," IEEE Transaction on Power Electronics, Vol. 31, No. 1, pp. 135–151, Jan. 2016.

- [2] Y. S. Lai and F. S. Shyu, "Topology for hybrid multilevel inverter," IEE Proceedings-Electric Power Applications, Vol. 149, No. 6, pp. 449–458, 2002.

- [3] M. R. Banaei, A. R. Dehghanzadeh, A. Fazel, and A. Baghbany Oskouei, "Switching algorithm for single Z-source boost multilevel inverter with ability of voltage control," IET Power Electronics, Vol. 6, No. 7, pp. 1350–1359, 2013.

- [4] J. Huang and K. A. Corzine, "Extended operation of flying capacitor multilevel inverters", IEEE Transactions on Power Electronics, Vol. 21, No. 1, pp. 140–147, 2006.

- [5] A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-point-clamped PWM inverter," IEEE Transaction on Industry Applications, Vol. IA-17, No. 5, pp. 518–523, Sep. 1981.

- [6] A. Shukla, A. Ghosh, and A. Joshi, "Natural balancing of flying capacitor voltages in multicell inverter under PD carrier-based PWM," IEEE Transactions on Power Electronics, Vol. 26, No. 6, pp. 1682–1693, 2011.

- [7] J. S. M. Ali, R. S. Alishah, and V. Krishnasamy, "A new generalized multilevel converter topology with reduced voltage on switches, power losses, and components," IEEE Journal of Emerging and Selected Topics in Power Electronics, Vol. 7, No. 2, pp. 1094–1106, 2018.

- [8] R. S. Alishah, D. Nazarpour, S. H. Hosseini, and M. Sabahi, "Reduction of power electronic elements in multilevel converters using a new cascade structure," IEEE Transactions on Industrial Electronics, Vol. 62, No. 1, pp. 256–269, 2015.