# INTERNATIONAL JOURNAL OF APPLIED SCIENCE ENGINEERING AND MANAGEMENT

E-Mail : editor.ijasem@gmail.com editor@ijasem.org

www.ijasem.org

# ENHANCING PERFORMANCE CHARACTERISTICS OF INDUCTION MOTORS WITH ADVANCED INVERTER TOPOLOGIES

<sup>1</sup>M.Rajyalakshmi,<sup>2</sup>MD.Younus,<sup>3</sup>J.Nageswara Rao,<sup>4</sup>Boddu Madhavi <sup>1,3</sup>Assistant Professor,<sup>2</sup>Associate Professor,<sup>4</sup>Student Department of EEE G V R & S College of Engineering & Technology,Guntur,AP

## ABSTRACT

This paper presents the simulation and implementation of multilevel inverter fed induction motor drive. The output harmonic content is reduced by using multilevel inverter. In symmetrical circuit, the voltage and power increase with the increase in the number of levels of inverter. The switching angle for the pulse is selected in such way to reduce the harmonic distortion. This drive system has advantages like reduced total harmonic distortion and higher torque. The model of the multilevel inverter system is developed with PWM strategy to control the induction motor. The rate of change of voltage with respect to time i.e. dv/dt is very high at these edges, of the order of 500-5000 V/µs.The two-level inverter topology has attracted attention in low power low voltage drive applications where as Three-Level inverter topology has attracted attention in high power High performances voltage drive applications. Single-phase VSI cover low-range power applications and three-phase VSI cover the medium- to high-power applications. The Main purpose of these three level inverter topologies is to provide a three-phase voltage source, where the amplitude, phase, and frequency of the voltages should always be controllable. Although most of the applications require sinusoidal voltage waveforms Key words :Medium-voltage ac drives, multilevel converter topologies.

## INTRODUCTION

Multilevel converters are considered for highpower medium-voltage drive applications, because the power structure can be realized with devices of lower voltage ratings [1]– [10]. A five-level inverter structure by cascading conventional two-level and three-level inverters is proposed in Part I of this paper [20]. An openloop control scheme is presented in Part I to maintain dc-link capacitor voltage balancing and common-mode voltage (CMV) elimination in a dual five-level inverter-fed open-end winding induction motor (IM) drive, which effectively uses only the available redundant switching states of the inverter. It is pointed out that the proposed open loop controller is unable to take any corrective action to reduce the unbalance in the capacitor voltages that may arise. Every individual inverter is capable of generating three different voltage output +Vdc ,0, -Vdc by connecting the dc source to the ac output side by different combinations of the four switches S1, S2, S3 and S4 [1]. The synthesize ac output voltage waveform of the sum of all the individual inverter's outputs. The number of output phase voltage level of cascade multilevel inverter is 2s+1 where S is the number of dc sources. This outstandingly increases the level number of the output wave form and thereby dramatically reduced to the low order harmonics and total harmonic distortion. One of the foremost motives for developing the multilevel inverter is to reduce costSimilar voltage profiles can also be obtained by using higher order neutral-point-clamped (NPC) multilevel inverters or by cascading a number of two-level inverters. However, the multilevel NPC inverters suffer from dc-bus imbalance, device underutilization problems and unequal ratings of the clamped diodes, etc., which are not very serious problems for inverters with three levels or lower. The capacitor voltage imbalance for a five-level one is presented in which suggest the need of extra hardware in the form of dc choppers or a back-to-back connection of multilevel converters. The cascaded H-bridge

topology suffers from the drawbacks of the usage of huge dc-bus capacitors and complex input transformers for isolated dc bus for each module. These drawbacks are addressed in the proposed topology. Furthermore, the power circuit is modular in structure, and hence, the number of modules to be connected in series depends on the power of the drive.

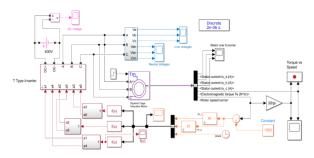

## PROPOSED CONVERTER TOPOLOGY

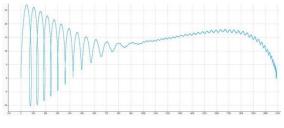

The proposed general configuration of "n" number of three level inverters connected in series is shown in Fig. 1. Each inverter module is a three-phase NPC three-level inverter. At the output stage, transformers are used to have the series connection of three-level inverters, as shown in Fig. 1. If "Vdc" is the dc-bus voltage of each inverter module, then " $\alpha$ " is the turns ratio of each transformer and "n" is the number of inverter modules then for sine PWM (SPWM) strategy; the motor rms phase voltage (VPh\_motor) can be expressed as follows Rms of Vph motor = $\sqrt{3} \alpha mnV dc/(2\sqrt{2})$  Where m is the modulation index of the inverter topology defined follows m=(Peak as of V\_(ph\_inverter))/(n V\_dc/2) Vph\_inverter is the total phase voltage reference of the inverter topology. For the given peak of VPh\_motor, peak of Vph\_inverter can be computed as follows Peak of V\_(ph\_inverter)=(Peak of V (ph motor))/( $\sqrt{3}$  a) The generation of individual reference voltage signal of each inverter is discussed as follows. The gate pulses for each three-level inverter module can be derived using two carrier signals. Thus, "n" numbers of such three-level inverter modules require "2n" number of carriers [10], [13]. The three-phase voltage reference signals are then compared with these carrier waves to produce the gate pulses for the inverters. For example, the carrier waves and the sinusoidal modulating voltage signal (SPWM technique) for R phase is shown in Fig. 2 for four series-connected threelevel inverters. The carrier waves 1 and 1\_ (Fig. 2) with R-phase voltage reference controls the inverter module 1. Similarly, 2 2\_, 3-3\_, and 4-4\_ carrier waves with R-phase voltage reference generate the gate pulses for the three-level

ISSN2454-9940

www.ijasem.org

inverter modules 2, 3, and 4, respectively. Thus, each inverter module produces the voltage proportional to a part of the reference phase voltage signals. It is important to note that no two three-level inverter modules switch simultaneously. Thus, the maximum dv/dt rate of the output voltage of this topology is limited to that of a single three-level inverter module.

Fig 1 Proposed circuit configuration

#### TABLE-I (SWITCHING TABLE)

| Generation of<br>Level | Switching Devices |     |     |           | Output  |

|------------------------|-------------------|-----|-----|-----------|---------|

|                        | <b>T1</b>         | T2  | T3  | <b>T4</b> | Voltage |

| +Vdc/2                 | on                | off | On  | off       | +1v     |

| 0                      | off               | on  | On  | off       | 0v      |

| -Vdc/2                 | off               | on  | Off | on        | -1v     |

Neutral Voltages

www.ijasem.org

#### Vol 12, Issue.4 Dec 2018

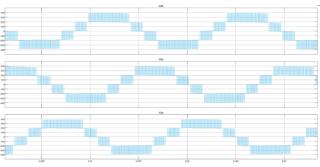

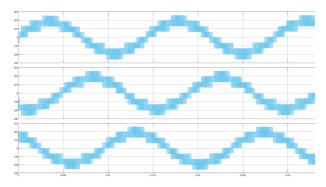

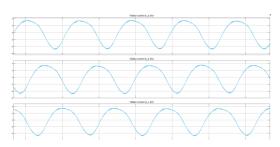

Stator Line Currents

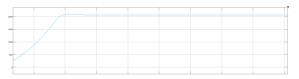

No Load Torque vs Slip

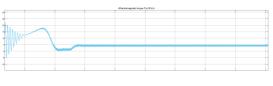

Figure (A)

### CONCLUSION

A simulation model of systems consisting of a multilevel inverter and an induction machined has been developed a series connection of three-level inverters has been proposed for a medium-voltage SQIM drive with increased voltage capacity. The topology

ensured high-power operations with mediumvoltage output having several voltage levels. The reduction in the ratings of the dc bus capacitor and reduced imbalance problems in the dc bus are some of the advantages of the proposed topology over the existing topologies. The disadvantage of the proposed topology is that it requires additional output transformers which introduce additional cost and losses. However, these transformers do not have complex underutilized windings like that required in cascaded H-bridge topologies. In this paper conventional and the cascaded multilevel inverter topologies were discussed and results were placed. Finally a Matlab/Simulink model is developed and simulation results are presented.

### REFERENCE

1. F. Wang, "Motor shaft voltages and bearing currents and their reduction in multilevel medium-voltage PWM voltage-source-inverter drive applications," IEEE Trans. Ind. Appl., vol. 36, no. 5, pp. 1336–1341, Sep./Oct. 2000.

2. S. Chen and T. A. Lipo, "Bearing currents and shaft voltages of an induction motor under hard- and soft-switching inverter excitation," IEEE Trans. Ind. Appl., vol. 34, no. 5, pp. 1042–1048, Sep./Oct. 1998.

3. L. M. Tolbert, F. Z. Peng, and T. G. Habetler, "Multilevel converters for large electric drives," IEEE Trans. Ind. Appl., vol. 35, no. 1, pp. 36– 44, Jan./Feb. 1999.

4. A.Muetze and A. Binder, "Calculation of circulating bearing currents in machines of inverter-based drive systems," IEEE Trans. Ind. Electron., vol. 54, no. 2, pp. 932–938, Apr. 2007.

5. J. Rodriguez, J. S. Lai, and F. Z. Peng, "Multilevel inverters: A survey of topologies, control and applications," IEEE Trans. Power Electron., vol. 49, no. 4, pp. 724–738, Aug. 2002.

6. P.W. Hammond, "A new approach to enhanced power quality for medium voltage

ISSN2454-9940

www.ijasem.org

#### Vol 12, Issue.4 Dec 2018

drives," IEEE Trans. Ind. Appl., vol. 33, no. 1, pp. 202–208, Jan./Feb. 1997.

7. R. Teodorescu, F. Blaabjerg, J. K. Pederson, E. Cengelci, and P. N. Enjeti, "Multilevel inverter by cascading industrial VSI," IEEE Trans. Ind. Electron., vol. 49, no. 4, pp. 832– 838, Aug. 2002.

8. A.Nabae, I. Takahashi, and H. Akagi, "A new neutral point clamped inverter," IEEE Trans. Ind. Appl., vol. 17, no. 5, pp. 518–523, Sep./Oct. 1981.

9. J.-S. Lai and F. Z. Peng, "Multilevel converters—A new breed of power converters," IEEE Trans. Ind. Appl., vol. 32, no. 3, pp. 509–517, May/Jun. 1996.

10. G. Cararra, S. Gardella, M. Marchesoni, R. Salutari, and G. Sciutto, "A new multilevel PWMmethod: A theoretical analysis," IEEE Trans. Power Electron., vol. 7, no. 3, pp. 497–505, Jul. 1992.

11. A.M. Trzynadlowski, R. L. Kirlin, and S. Legowski, "Space vector PWM technique with minimum switching losses," IEEE Trans. Ind. Electron., vol. 44, no. 2, pp. 173–181, Apr. 1997.

12. Y. S. Lai and S. R. Bowes, "Optimal busclamped PWM techniques for threephase motor drives," in Proc. Annu. Conf. IEEE Ind. Electron. Soc., Busan, Korea, Nov. 2–6, 2004, pp. 1475–1480.

13. Suvajit Mukherjee and Gautam Poddar "A Series-Connected Three-Level Inverter Topology for Medium-Voltage Squirrel-Cage Motor Drive Applications" Ieee Transactions On Industry Applications, Vol. 46, No. 1, January/February 2010.